安兔兔得分破3万6,Tegra 4/4i、i500基带再解

- 电子产品

- 2021-07-05

- 276

- 更新:2021-07-05 14:28:01

对于NVIDIA发布的Tegra4以及后来的Tegra4i,我们已经了解了不少了,前者是世界首款四核Cortex-A15处理器,官方表示其性能非常强劲,加载网页的速度已经超过了目前最强的苹果A6X。

Tegra

4i处理器的CPU架构则返璞归真到了Cortex-A9,但是NVIDIA表示它与普通的A8架构也不一样,也是做了改进的。除此之外,Tegra4的GPU以及icera

i500基带以及Tegra4/4i智能设备的公版设计——Phoenix平台也值得期待。

时隔一个多月后,NVIDIA又公布了一些Tegra

4/4i架构设计的详细资料,并且有一张官方的性能测试表,我们熟知的安兔兔跑分高达36000多,让人十分惊讶,我们借着Anandtech网站的相关分析再来一探Tegra

4的强大之处。

原文分了很多页,这里为了行文方便,重新排列了分页。

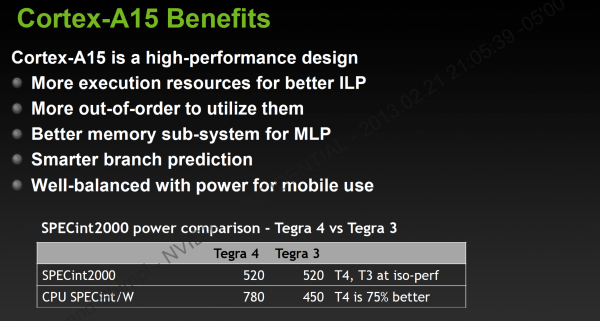

CPU架构:Cortex-A15的利与弊

首先来看Tgera4的,它是基于ARM

Cortex-A15架构设计的,专为性能而生,而ARM处理器中主打功耗比的则是Cortex-A7。根据之前的资料,A15架构的性能是A7的三倍,不过核心面积和功耗也达到了后者的4倍和6倍。

NVIDIA给出的A15优点如上图所示,它拥有更多的执行单元、更优秀的分支预测设计以及更强的内存子系统。

NVIDIA首先将Tegra4与Tegra3按照同样的SPECint2000测试测试配置好了,二者成绩都是520分,然后再对比二者的功耗,Tgera

4的每瓦SPECint性能是780,而Tegra3只有450,T4比T3强了75%,也就是说如果在同样的性能下,A15架构的T4相比T3节省了40%的功耗。

当然了,这项对比也不完全公平,Tegra3的是运行在最高1.6GHz频率上的,对功耗要求自然比较高,而Tegra

4是限制频率的,大约只有825MHz,更低的频率意味着更低的电压,这可以降低功耗,换句话说NVIDIA在这里的对比虽然很有用,但这是一个小花招,有可能造成消费者的误解。

从这里也可以看出NVIDIA准备如何将Tegra

4带到手机领域,那就是大幅降低其频率。如果825MHz的T4已经可以达到40nm工艺下的A9架构1.6GHz频率下的性能,那么实际应用中低频的T4也许就不会突破现有的功耗需求了。

825MHz的频率也会变得很重要,因为Tegra

4处理器的第五个核心(同为A15架构)最高运行频率就是825MHz,假设NVIDIA能将这颗伴生核心的频率一直运行在825MHz,那么T4(用在手机上时)的典型功耗或许还不会让人很担心,不过峰值功耗依然会是一个问题。

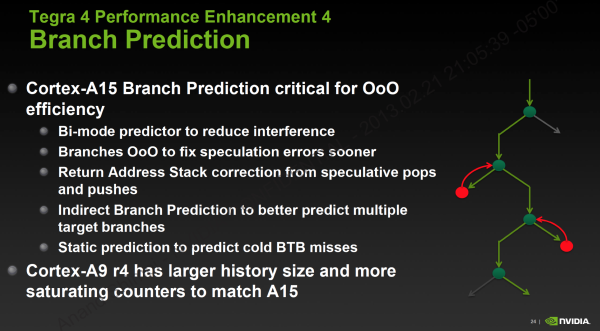

Cortex-A15架构设计

A15架构的特点之前已经有过介绍,这里再来详细看一下。与Cortex-A9架构相比,其整数流水线从9级提高到了15级,这样可以提高处理器频率,不过长流水线也需要更强的分支预测设计。

与A9架构相比,A15的前端提升了50%,而指令预取(Fetech)带宽加倍,可以提高指令的并行性。另外,为了充分利用3发射(3-wide)的能力,ARM极大地提升了重排序缓冲器(reorder

buffer)以及相关数据结构部分的大小,举例来说,A9架构的重排序缓冲器可同时有32-40个解码指令,A15架构则提升到了128个,4倍于A9架构。

可以这么说,A9架构只是前一代A8架构的正常进化版,但是A15相比A9则是一次架构设计的飞跃,很明显ARM这样的设计并不单单是为了应付智能手机的需求。

再说执行单元,A15的设计也要比A9增强不少,前者的=拥有更多执行端口及执行单元,可以提升ILP(指令级并行)/单线程性能。ARM设计了多路、独立的指令发射队列(issue

queues)以保持处理器高频率运行,每个队列可以接收三条指令,而所有队列都可以并行运作。

A15架构的执行单元与A9一样是乱序执行(outoforder,简称OoO),但也做了改进。所有FP(浮点)/NEON(多媒体指令)在A9上都是顺序执行的,但是A15架构中就可以OoO方式执行。不过A5架构依然不能重排序内存操作,独立的Load操作可以乱序执行,但是Stores存储不能先于Load操作进行。

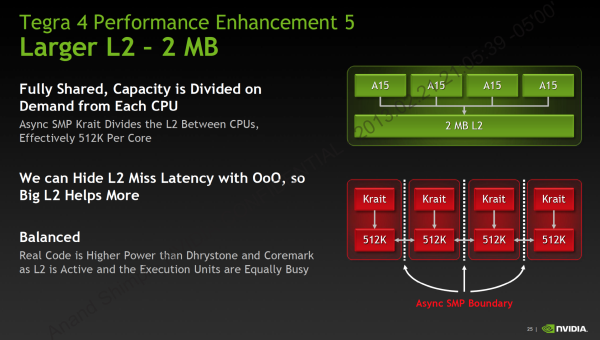

Cortex-A15架构重新回归到了集成L2缓存的路线,而不像A9那样使用的是独立IP单元。L1与L2缓存的延迟大体上不变,不过本文作者相信集成L2缓存相比A9的设计依然会有1-2周期延迟的惩罚。L2缓存的TLB及其他数据结构也做了相应的增加以匹配架构设计的变化。

此外,Tegra

4的L1缓存依然是A9架构的32KB指令+32KB数据的组合,不过其L2缓存增加到了2MB,四个内核共享L2缓存,而伴生核心拥有独立的512KBL2缓存。

北京私人放款有需要的联系我,老哥分享十款网贷多了综合评分不足怎么贷款才能通过

京东可以协商延期还款吗,网友收集十款征信黑了又有当前逾期可以从哪个平台借钱

怎么查看自己征信是否被清除了,专业解读十款负债高没有逾期可以申请什么贷款

不看征信不看大数据网贷百分百下款,本篇归档十款大数据花了综合评分不足哪里可以借钱

大数据花了综合评分不足怎么借钱,本文探讨十款羊小羊借款app下载发布日期

贷款逾期了怎么跟银行协商解决,网友收集十款大数据不好哪个平台可以借钱

征信不好没有资产怎么贷款,深度细说十款正规的网上借款平台都有哪些

什么软件综合评分不足也能借到钱,老哥分享十款征信不好哪里可以借钱 急用

企查查上的强制执行怎么消除,深度细说十款征信综合评分不足可以在哪个平台借到钱

上一篇:广西将启动5万吨铝锭收储计划

下一篇:在家具城工作